History

### ARC: Computer Architecture tanguy.risset@insa-lyon.fr Lab CITI, INSA de Lyon Version du January 24, 2023

Tanguy Risset

January 24, 2023

< 67 b

### Table of Contents

Processor Architecture

A 1

0000

# ARC course presentation

- Schedule:

- Course 8h

- small labs (TD) 6h

- labs (TP) 16h

- Evaluation (In french): un QCM et un devoir papier en fin de cours

- skills and knowledge learned in ARC cours:

- Bolean logic, arithmetics

- combinatorial and sequential logic circuits, automata.

- Processor architecture, datapath, compilation process, RISC architecture

- Assembly code, link with high level programming languages

- Simple processor design, simple assembly program analysis.

- Link with compilation, operating systems and programming

- Moddle (open): frames, labs, various document

- Course based on the two IF architecture course: AC and AO (open courses on Moodle).

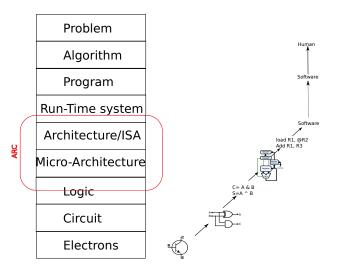

#### From electron to Von-Newman CPU

・ロト ・同ト ・ヨト ・ヨト

э

Processor Architecture

# Computer architecture usefulness

- How to solve a problem with electrons:

- ARC is useful

introduction

0000

- For general knowledge of a computer scientist

- To understand pro/cons of modern complex architectures

- For embedded system programming

#### Table of Contents

Processor Architecture

< E

A 1

Electrons and Logic

# History of computing

introduction

• Ancient time: various arithmetics systems

History

000

- 17th century (Pascal and Leibniz): notion of mechanical calculator

- 1822 Charles Babbage Difference engine (tabulate polynomial htt functions)

- 1854 Georges Boole proposes the so-called Boolean logic.

- (More details on the poly or on Internet)

from Yale Babylonian Collection,  $\simeq$  1600 BC

http://www.math.ubc.ca/~cass/Euclid/ybc/ybc.html

Difference Machine close-up

By By Carsten Ullrich - Own work, CC BY-SA 2.5

Processor Architecture

History 00● Electrons and Logic

Processor Architecture

# History of computers

- 1936: Alan Turing's PhD on a universal abstract machine

- 1941: Konrad Suze builds the Z3 first programmable computer (electro-mechanic)

- 1946: ENIAC is the first electronic calculator

- 1949: Turing and Von Neumann build the first universal electronic computer: the Manchester Mark 1

- (More details on the poly or on Internet)

Z3 computer at Deutches Museum, Munich

By Venusianer, CC BY-SA 3.0

### Table of Contents

#### Processor Architecture

- ∢ ≣ →

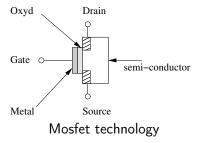

- Discovered in 1947 at Bell Labs: (transfer resistor)

- Could replace the thermionic triode (vacuum tube) that allow radio and telephone technologies.

- Principle: flow or Interrupt current between Source and Drain, depending on Gate status

- Can be seen as a switch

- Wildly used after Integrated Circuit invention (1958)

introduction

# Popular Transistor technology: CMOS

History

- CMOS: Complementary Metal Oxide Semiconductor

- Two logical levels : 0 = 0V and 1 = 3V

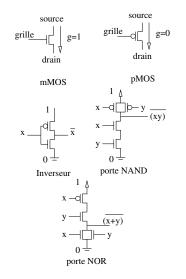

- Two types of transistors

- nMOS : current flows if gate is 1

- pMOS : current flows if gate is 0

- Mainly used to realize basic logical gates (NOT, NAND, NOR, etc.)

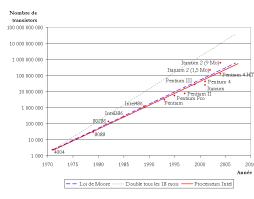

#### Moore's low

- Gordon Moore, co-founder of Fairchild Semiconductor and Intel, predicted in "a doubling every two year in the number of components per integrated circuit"

- Contributed to world economic growth

- Slow down in 2015 and should end soon.

Image: A mathematical states and a mathem

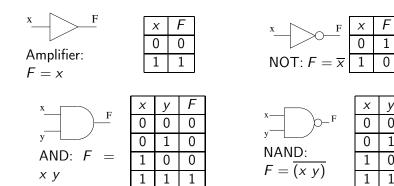

#### Boolean functions

Boole Algebra is equipped with three operations

- a unary operation, **negation**, noted NOT;

- two binary commutative, associative operations:

- conjunction AND, with 1 as neutral element;

- disjunction OR, with 0 as neutral element;

- AND is distributive over OR

If *a* and *b* are 2 boolean variables, we write:

$$\mathsf{NOT}(a) = \overline{a}, \quad \mathsf{AND}(a, b) = ab = a.b, \quad \mathsf{OR}(a, b) = a + b$$

introduction

#### Electrons and Logic

Processor Architecture

# Boolean Cheat Sheet

- neutral elements: a + 0 = a,  $a \cdot 1 = a$

- absorbing elements: a+1

- idempotence: a + a = a,  $a \cdot a = a$

- tautology/antilogy:

- commutativity:

- distributivity:

- associativity:

- De Morgan's law:

• others:

a+1=1,  $a \cdot 0 = 0$ a + a = a.  $a \cdot a = a$  $a + \overline{a} = 1$ .  $a \cdot \overline{a} = 0$ a + b = b + a, ab = ba $a + (bc) = (a + b)(a + c), \quad a(b + c) = ab + ac$ a + (b + c) = (a + b) + c = a + b + c. a(bc) = (ab)c = abc $\overline{ab} = \overline{a} + \overline{b}$  $\overline{a+b} = \overline{a} \cdot \overline{b}$ a + (ab) = a,  $a + (\overline{a}b) = a + b$ , a(a+b) = a,  $(a+b)(a+\overline{b}) = a$

- 4 同 6 4 日 6 4 日 6

Electrons and Logic

Processor Architecture

F

1

1

1

0

3

・ロト ・同ト ・ヨト ・ヨト

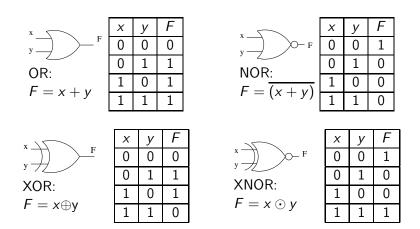

#### Elementary logical gates

#### Electrons and Logic

Processor Architecture

#### Elementary logical gates

・ロト ・同ト ・ヨト ・ヨト

3

Processor Architecture

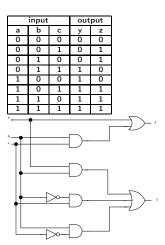

# Combinatorical circuit Design

- Boolean description of the problem:

- Compute y and z from a, b and c

- *y* is 1 if *a* is 1 or *b* and *c* are 1.

- z is 1 if b or c is 1 (but not both) or if a, b et c are 1.

- 2 Truth table

- Optimization Logic equation

•

$$y = \overline{a}bc + a\overline{b}\overline{c} + a\overline{b}c + ab\overline{c} + abc$$

- $z = \overline{a}\overline{b}c + \overline{a}b\overline{c} + a\overline{b}c + ab\overline{c} + abc$

- Optimized logic equations

- y = a + bc

- $z = ab + \overline{b}c + b\overline{c}$

Iogic gates

#### Disjunctive Normal Form (DNF)

- In Boolean logic, a logical formula in Disjunctive Normal Form (*Forme normale disjonctive* in French) if:

- It is a disjunction of one or more clauses

- where the clauses are conjunction of literals

- a literal is a variable, a constant or 'not' a variable

- Otherwise put, it is an OR of ANDs.

- Example of DNF:

- $x.\overline{y}.\overline{z} + \overline{t}.u.v$

- $(a \wedge b) \vee \neg c$

- Example not in DNF:

- $\overline{(x+y)}$

introduction

•  $a \lor (b \land (c \lor d))$

# Conjunctive Normal Form (CNF)

- In Boolean logic, a formula is in conjunctive normal form (*forme normale conjonctive* in French) if:

- it is a conjunction of one or more clauses,

- where a clause is a disjunction of literals;

- a literal is a variable, a constant or 'not' a variable

- Otherwise put, it is an AND of ORs.

- Example of CNF:

•

$$(x+\underline{y}+\overline{z})(\overline{x}+z)$$

- $(a+\bar{b}+\bar{c})(\bar{d}+\bar{a})$

- *x* + *y*

introduction

• Example not in CNF

•

$$\overline{(x+y)}$$

• x(y + (z.t))

#### ARC: Computer Architecture

Electrons and Logic

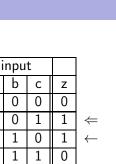

# From Truth table to DNF

History

introduction

- Back to previous example (z is 1 if b or c is 1 (but not both) or if a, b et c are 1.)

- Truth table on the right, z is 1 if and only if one of the five condition identified occurs.

- It is easy to find a conjunction that is valid in a unique case: example:  $\bar{a}.\bar{b}.c$  is 1 if and only if: a = 0, b = 0 and c = 1 (double arrow on the right)

- by adding all the conjunction valid only on each of the five cases identified on the right, we get a DNF formulae that has exactly that truth table.

Hence the possible formulae for z:  $z = \overline{abc} + \overline{abc} + \overline{abc} + \overline{abc} + \overline{abc} + \overline{abc}$ How can it be simplified?

1

$\leftarrow$

n

а

0

0

0

0

1 0

0 0 0

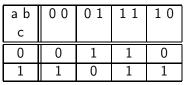

# Simple Boolean optimization: Karnaugh Table (1)

Karnaugh map (tables de Karnaugh) use a "visual" reprentation of a simple property:

Electrons and Logic

$(a.\overline{b})+(a.b)=a.(\overline{b}+b)=a$

History

introduction

- The first step in the method is to transform the truth table (3 or 4 input variables) of the function in a two-dimensional array (split into two parts of the set of variables)

- Rows and columns are indexed by the valuations of the corresponding variables in such a way that between two rows (or columns) only one boolean value changes.

- In our example (3 variables):

# Simple Boolean optimization: Karnaugh Table (2)

• Then, we try to cover all '1' of the table by forming groups.

Electrons and Logic

• each group contains only adjacent '1'

History

- must form a rectangle

- the number of elements of a group must be a power of two.

- each group correspond to a possible optimization of the DNF

| a b | 00 | 01 | 11 | 10 |

|-----|----|----|----|----|

| с   |    |    |    |    |

| 0   | 0  | 1  | 1  | 0  |

| 1   | 1  | 0  | 1  | 1  |

• In our example:

introduction

- example : Three groups:

- $\bar{a}.b.\bar{c} + a.b.\bar{c}$  simplifies to  $b.\bar{c}$

- $a.b.\overline{c} + a.b.c$  simplifies to a.b

- $a.\overline{b}.c + \overline{a}.\overline{b}.c$  simplifies to  $\overline{b}.c$

#### • hence $z = \overline{abc} + \overline{abc} + \overline{abc} + \overline{abc} + \overline{abc} + \overline{abc}$ simplifies to $z = a.b + \overline{b.c} + b.\overline{c}$

# Well formed cicruits

As far as combinatorial circuits are concerned, a "Well formed" circuit is:

- A logic gate

- A wire

- Two well formed circuits next to each other

- Two well formed circuits, the outputs of one being the inputs of the other

- Two well formed circuits sharing a common input

- It can be shown that it correspond to an acyclic graph of logic gates.

- No cycles, no ouptuts conected together

### Usefull combinatorics logic components

- *n* input multiplexer

- decoder  $log(n) \rightarrow n$

- *n* bits adder

- *n* bits comparator

- n bits ALU

- etc.

introduction

A □ > A □

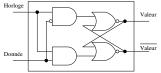

### Memorizing: latches and Flip-Flops

History

Set-Reset Latch (SR latch, Bascule RS): When R and S are reset, Q and Q keep their previous value.

Electrons and Logic

introduction

| S | R | Q         | $\overline{Q}$       |

|---|---|-----------|----------------------|

| 0 | 1 | 0         | 1                    |

| 1 | 1 | forbidden | forbidden            |

| 1 | 0 | 1         | 0                    |

| 0 | 0 | $Q_{n-1}$ | $\overline{Q_{n-1}}$ |

- Bascule RS

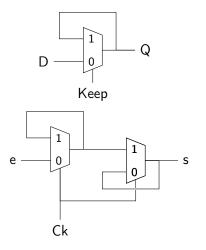

- Gated D latch (Flip-flop, register, *Bascule D*): sample input data on clock rising edge and keeps the value when clock is 0.

introduction History Cectrons and Logic Processor Architecture

#### latches and Flip-Flops: other common representation

• Latch (*verrou*)

• Flip-Flop (register)

# Sequential logic

introduction

Sequential logic combines logic function and memorizing, it opens the way to synchronous circuits, automata, programs, algorithms....

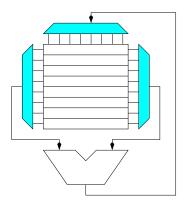

- *n* bits register

- *n* bits counter

- state machine

- OPU

- Computer

Image: A (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) → (1) →

#### Sequential circuit design

- Extremely complex in general.

- Many computation models:

- Sequential

- State machine

- control + data-path

- task parallelism (communicating tasks)

- Data parallelism (data-flow)

- Asynchronous circuits

- Important notion use every where: finite state machine (automate)

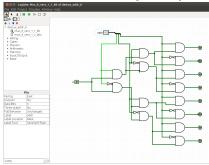

# Logic in ARC: Logisim

In ARC: use of logisim software (http://www.cburch.com/logisim/)

- Design basic logic components (TD1)

- Design of a memory (sequential component, TD2)

- Design of dedicated circuit: integer division (TD3).

Image: A math a math

### Table of Contents

A 1

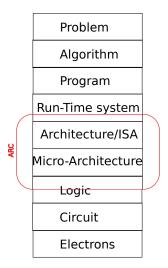

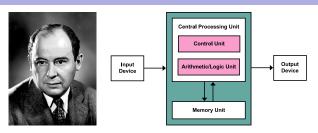

introductionHistoryElectrons and LogicProcessor ArchitectureWhat is a Von Neumann machine?

- Computer architecture Model (also called *Princeton* architecture) proposed after J. Von Neumann report: "First Draft of a Report on the EDVAC".

- Usually abstracted as a processor connected to a memory

- The memory is accessed (*randomly*) with an address (i.e. unlike a Turing machine)

- The memory contains both data and program (unlike a Harvard machine).

#### How does it work?

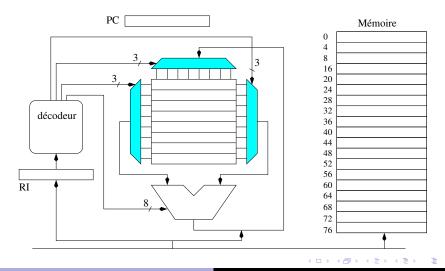

Compilation, Assembly code and binary code

| $High \ Level \ Language \Rightarrow$ | Assembly code $\Rightarrow$ | $Binary  \operatorname{code} \Rightarrow$ |

|---------------------------------------|-----------------------------|-------------------------------------------|

| int a,b,c;                            | load RO, @b                 | 0100101110101                             |

| a = b + c;                            | load R1, @c                 | 0100101010001                             |

|                                       | add R3,R0,R1                |                                           |

|                                       | store R3, @a                | 1001001100011                             |

|                                       |                             |                                           |

э

・ロト ・同ト ・ヨト ・ヨト

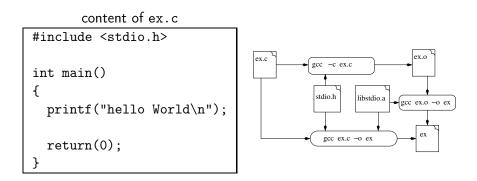

# Fast compilation thanks to Donald Knuth (and others..)

• The programmer:

introduction

- Write a program (say a C program: ex.c)

- Compiles it to an object program ex.o

- links it to obtain an executable ex

< A → < 3

B → B

Mémoire

Tanguy Risset

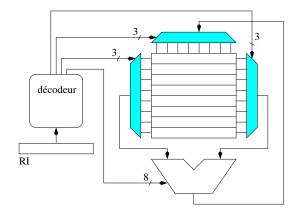

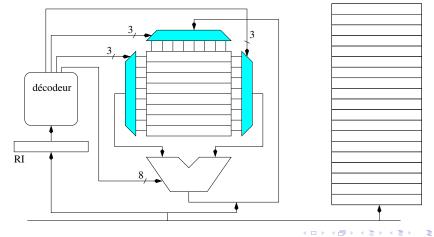

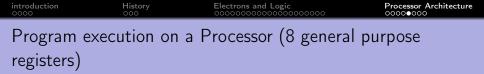

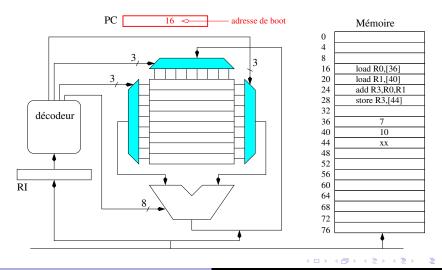

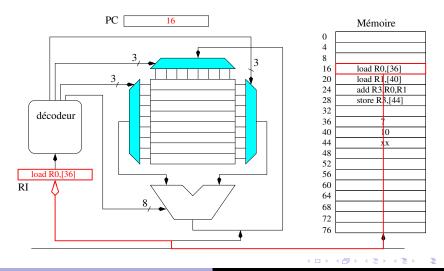

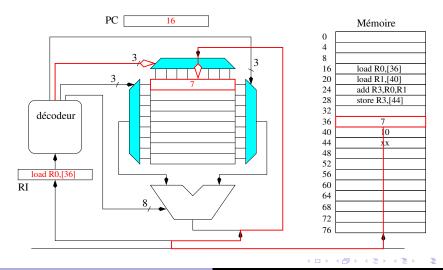

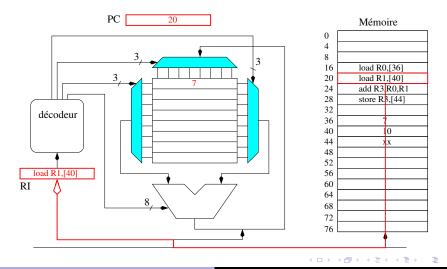

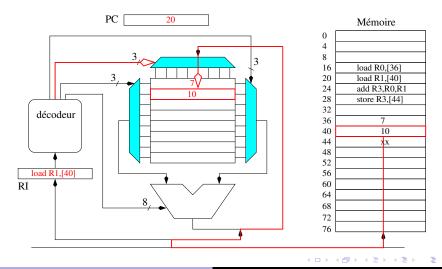

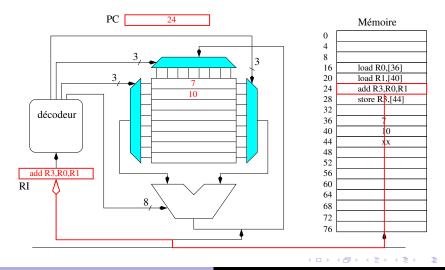

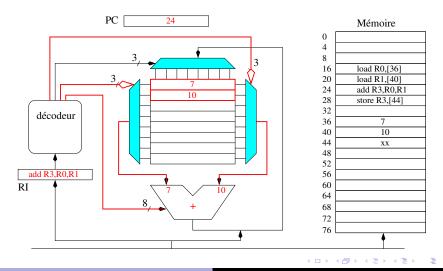

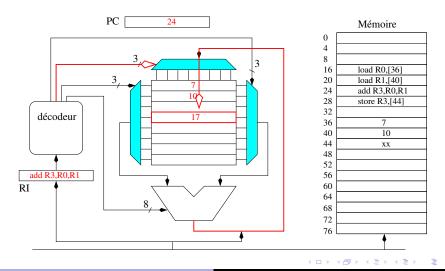

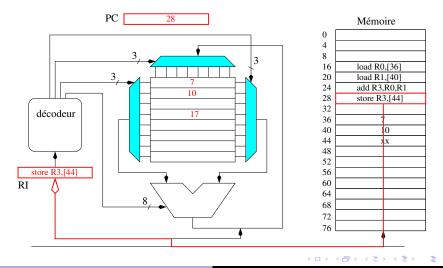

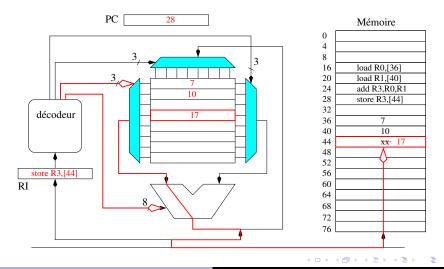

introductionHistoryElectrons and LogicProcessor ArchitectureProgram execution on a Processor (8 general purposeregisters)

## Program execution on a Processor (8 general purpose registers)

Tanguy Risset

Tanguy Risset

## Computer Architecture in ARC

- Design of a simple dedicated circuit in logisim

- Study of a simple processor in logisim

- Overview of assembly code principles

- Compilation basics

introduction

• embedded system case study

## Add on: two's complement representation

History

- Two's complement (*complément à deux*) is the most common representation for negative integers

- For a number on N bits:

introduction

• Positive integers from 0 to  $2^{N-1} - 1$  are represented with usual binary encoding

Electrons and Logic

- Negative integer x from -2<sup>N-1</sup> to -1 are represented by coding in binary the positive number 2<sup>N</sup> - |x|

- Hence Negative integers always have the last (i.e. most significant) bit at 1, and positive always have the last bit at 0

- Example with N = 3

- $\bullet\,$  Integers between  $-4_{10}$  and  $3_{10}$  can be represented

- $-1_{10}$  is represented as  $111_2 (2^3 1 = 7)$

- $-2_{10}$  is represented as  $110_2 (2^3 2 = 6)$

- $-4_{10}$  is represented as  $100_2 (2^3 4 = 4)$

Processor Architecture

## Add on: two's complement representation (2)

• Two's complement have an important property: Addition "classical" algorithm works (except that the overflow should be ignored).

Electrons and Logic

• Example:

introduction

- $-1_{10} + (-2_{10}) = 111_2 + 110_2 = 1101_2 =$ (ignoring the carry/overflow) $101_2 = -3$

- $-1_{10} + 2_{10} = 111_2 + 010_2 = 1001_2 =$ (ignoring the carry/overflow)001\_2 = 1

- For x > 0,  $x \le 2^{N-1}$ , The representation of -x on N bit two's complement can be obtained by:

- Complementing each bits of x

- adding 1 to the resulting integer

History

- Example:

- with N = 3 and  $x = 3_{10} = 011_2$ , complement of x is  $100_2$  adding 1 gives  $101_2 = -3_{10}$

- With N=8 and  $x = 96_{10} = 01100000_2$  complement of x is 10011111, adding one is  $-96_{10} = 10100000_2$ , indeed  $256 96 = 160 = 10100000_2$